#### **Feature**

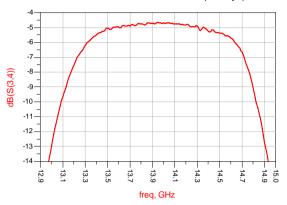

Pass Bands: 12.2GHz ~ 13.4GHz, 13.4GHz ~ 14.6GHz;

Insertion Loss in pass bands: ≤8dB Isolation between pass bands: ≥30dB

Size: 4.5x4.0x0.15mm

# Description

This device is a FET switch filter bank MMIC based on GaAs processing. Adopt +5V/0V logic control, switching time is less than 30ns typ. It has low loss, excellent isolation, and high integration.

The metallization processing of thru-holes on the plate ensures good grounding. Extra grounding measures aren't required, which is easy for application. The back metallization is suitable for eutectic sintering or conductive adhesive sticking processes.

### **Absolute Rating**

| Control Voltage       | -1V~+5V           |  |

|-----------------------|-------------------|--|

| Input Power           | Input Power 27dBm |  |

| Storage Temperature   | -65~+150°C        |  |

| Operating Temperature | -55~+125℃         |  |

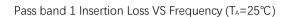

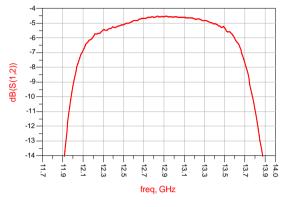

# **Electrical Specifications 1** (T<sub>A</sub>=+25°C)

| Spec.          | Pass band 1 | Pass band 2 | Unit |

|----------------|-------------|-------------|------|

| Freq. Range    | 12.2~13.4   | 13.4~14.6   | GHz  |

| Insertion Loss | ≤8          | <b>≤</b> 8  | dB   |

| Rejection      | ≥35@10.8GHz | ≥35@12GHz   | dBc  |

|                | ≥15@14GHz   | ≥15@15.2GHz | dBc  |

| VSWR           | ≤2          |             | _    |

S2P file name: PDSBF2-12R2\_14R6.s2p

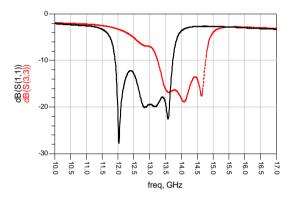

# **Typical Test Curves**

Pass band 2 Insertion Loss VS Frequency (T<sub>A</sub>=25°C)

Insertion Loss VS Frequency (T<sub>A</sub>=25°C)

Return Loss VS Frequency (T<sub>A</sub>=25°C)

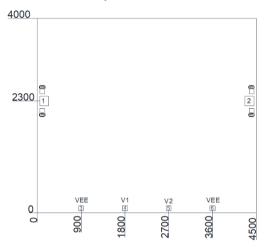

## **Mechanical Specification**

#### **Truth Table**

| Driver Voltage (VEE=-5V)         |    | Pass bands   |  |  |

|----------------------------------|----|--------------|--|--|

| V1                               | V2 | Pass Danus   |  |  |

| 5V                               | 0V | 12.2-13.4GHz |  |  |

| 0V                               | 5V | 13.4-14.6GHz |  |  |

| Status: Low (0) 0V; High (1) +5V |    |              |  |  |

#### **PINS Definitions**

| Pin No. | Symbol   | Description                    |

|---------|----------|--------------------------------|

| 1, 2    | RF1, RF2 | RF Input, RF Output            |

| 3, 6    | VEE      | Driver Power Supply<br>Voltage |

| 4, 5    | V1, V2   | Control ports                  |

#### Notes:

- 1. Dimensions are um. Tolerance: ±0.05mm

- 2. Die thickness is 0.1mm

- 3. Typical bond pad is 100um \*100um, which is 50um away from chip edge.

- 4. The bottom of the device is gold plated, should be grounded.

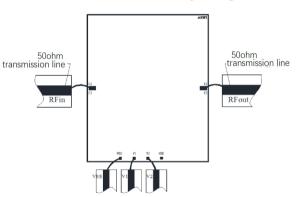

# **Recommended Assembly Diagrams**

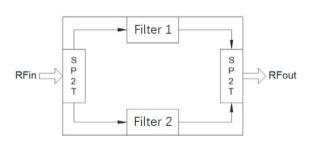

# **Functional Diagram**

### **Application Notes:**

- 1. The chip is back-metallized and can be die-mounted with AuSn eutectic preforms or with electrically conductive epoxy.

- 2. The die should be assembled on carriers like Kovar or Mu-Cu which have same Coefficient of thermal expansion. ( $5.8 \times 10$ -6/) with GaAs.

- 3. Recommend using  $\Phi$ 25um Au wire for bonding, whose length is around 200um.

- 4. Sinter by AuSn (80/20), which doesn't exceed 300°C within 30 seconds max.

- 4. Handle the chips in a clean environment. DO NOT attempt to clean the chip using liquid cleaning systems.

- 5. Handle the chip along the edges with a vacuum collet or with a sharp pair of bent tweezers.

- 6. The device is sensitive to ESD. ESD protection is required during storage and usage.

- 7. If you have any questions, please contact us.